### MOS LSI

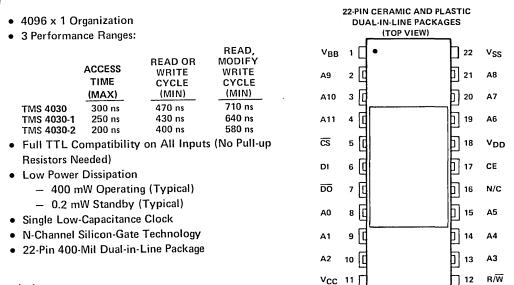

### TMS 4030 JL, NL; TMS 4030-1 JL, NL; TMS 4030-2 JL, NL 4096-BIT DYNAMIC RANDOM-ACCESS MEMORIES

BULLETIN NO. DL-S 7512240, FEBRUARY 1975

### description

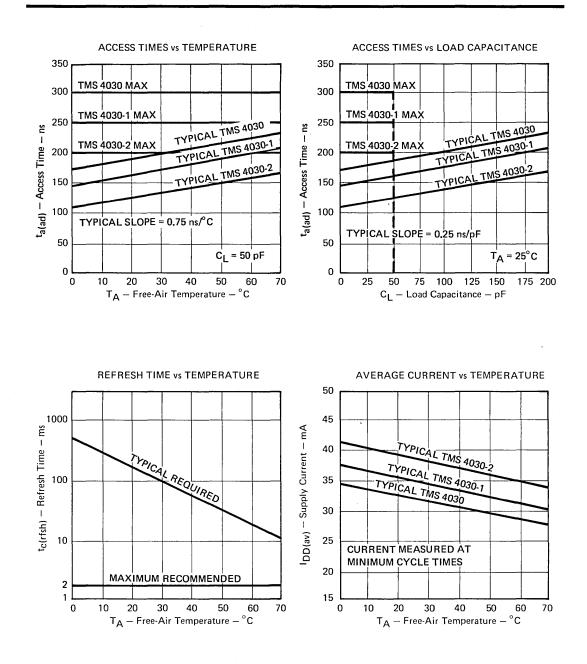

The TMS 4030 series is composed of high-speed dynamic 4096-bit MOS random-access memories, organized as 4096 one-bit words. N-channel silicon-gate technology is employed to optimize the speed/power/density trade-off. Three performance options are offered: 300 ns access for the TMS 4030, 250 ns access for the TMS 4030-1, and 200 ns for TMS 4030-2. These options allow the system designer to more closely match the memory performance to the capability of the arithmetic processor.

All inputs except the chip enable are fully TTL-compatible and require no pull-up resistors. The low capacitance of the address and control inputs precludes the need for specialized drivers. When driven by a Series 74 device, the guaranteed dc input noise immunity is 200 mV. The TTL-compatible buffer is guaranteed to drive two Series 74 TTL gates. The TMS 4030 series uses only one clock (chip enable) to simplify system design. The low-capacitance chip-enable input requires a positive voltage swing (12 volts), which can be driven by a variety of widely available drivers.

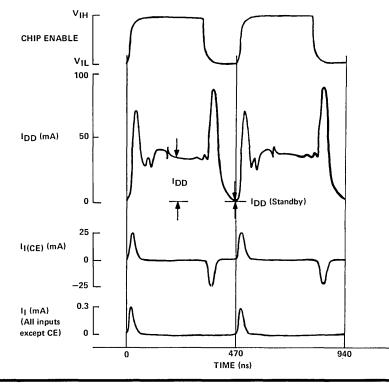

The typical power dissipation of these RAM's is 400 mW active and 0.2 mW standby. To retain data only 6 mW average power is required, which includes the power consumed to refresh the contents of the memory.

The TMS 4030 series is offered in both 22-pin ceramic (JL suffix) and plastic (NL suffix) dual-in-line packages. The series is guaranteed for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. These packages are designed for insertion in mounting-hole rows on 0.400-mil centers.

### operation

### chip select $(\overline{CS})$

The chip-select terminal, which can be driven from standard TTL circuits without an external pull-up resistor, affects the data-in, data-out and read/write inputs. The data input and data output terminals are enabled when chip select is low. Therefore, the read, write, and read, modify write operations are performed only when chip select is low. If the chip is to be selected for a given cycle, the chip-select input must be low on or before the rising edge of the chip enable. If the chip is not to be selected for a given cycle, chip select must be held high as long as chip enable is high. A register for the chip-select input is provided on the chip to reduce overhead and simplify system design.

### chip enable (CE)

A single external clock input is required. All read, write, and read, modify write operations take place when the chip enable input is high. When the chip enable is low, the memory is in the low-power standby mode. No read/write operations can take place because the chip is automatically precharging.

PRELIMINARY DATA SHEET: Supplementary data may be published at a later date.

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 • DALLAS, TEXAS 75222

### operation (continued)

### mode select (R/W)

The read or write mode is selected through the read/write  $(R/\overline{W})$  input. A logic high on the  $R/\overline{W}$  input selects the read mode and a logic low selects the write mode. The read/write terminal can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected.

### address (A0-A11)

All addresses must be stable on or before the rising edge of the chip-enable pulse. All address inputs can be driven from standard TTL circuits without pull-up resistors. Address registers are provided on chip to reduce overhead and simplify system design.

#### data-in (DI)

Data is written during a write or read, modify write cycle while the chip enable is high. The data-in terminal can be driven from standard TTL circuits without a pull-up resistor. There is no register on the data-in terminal.

#### data-out (DO)

The three-state output buffer provides direct TTL compatibility with a fan-out of two Series 74 TTL gates. The output is in the high-impedance (floating) state when the chip enable is low. It remains in the high-impedance state if the chip-select input is high when chip enable goes high and provided that chip select remains high as long as chip enable is high. If the chip select is set up low prior to the rise of chip enable and held low an interval after that rise, the output will be enabled as long as chip enable stays high regardless of subsequent changes in the level of chip select. A data-valid mode is always preceded by a low output state. Data-out is inverted from data-in.

### refresh

Refresh must be performed every two milliseconds by cycling through the 64 addresses of the lower-order-address inputs, A0 through A5 (pins 8, 9, 10, 13, 14, 15), or by addressing every row within any 2-millisecond period. Addressing any row refreshes all 64 bits in that row. The chip does not need to be selected during the refresh. If the chip is refreshed during a write mode, then chip select must be high. The column addresses (A6 through A11) can be indeterminate during refresh.

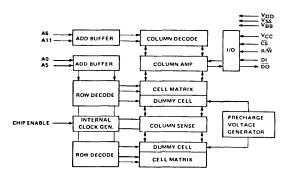

### functional block diagram

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note)                                                         |    |    |   |  |  |   |  |  |     |     |                  |     |      |       |      | 0.3 to 20 V        |

|----------------------------------------------------------------------------------------------------|----|----|---|--|--|---|--|--|-----|-----|------------------|-----|------|-------|------|--------------------|

| Supply voltage, VDD (see Note)                                                                     |    |    |   |  |  |   |  |  |     |     |                  |     |      |       |      | 0.3 to 20 V        |

| Supply voltage, V <sub>SS</sub> (see Note)                                                         |    |    |   |  |  |   |  |  |     |     |                  |     |      |       |      | 0.3 to 20 V        |

| All input voltages (see Note)                                                                      |    |    |   |  |  |   |  |  |     |     |                  |     |      |       |      |                    |

| Chip-enable voltage (see Note)                                                                     |    |    |   |  |  |   |  |  |     |     |                  |     |      |       |      | 0.3 to 20 V        |

| Output voltage (operating, with respect to                                                         | νc | SS | ) |  |  |   |  |  |     |     |                  |     |      |       |      | –2 to 7 V          |

| Operating free-air temperature range .                                                             |    |    |   |  |  |   |  |  |     |     |                  |     |      |       |      |                    |

| Storage temperature range                                                                          |    |    |   |  |  | - |  |  |     |     |                  |     |      |       |      | –55°C to 150°C     |

| NOTE: Under absolute maximum ratings, voltage valu<br>noted. Throughout the remainder of this data |    |    |   |  |  |   |  |  | olt | age | , ∨ <sub>€</sub> | 3 B | (sut | ostra | ate) | , unless otherwise |

recommended operating conditions (see Note)

| PARAMETER                                                               | MIN                  | NOM | MAX     | UNIT |

|-------------------------------------------------------------------------|----------------------|-----|---------|------|

| Supply voltage, V <sub>CC</sub>                                         | 4.75                 | 5   | 5.25    | V    |

| Supply voltage, VDD                                                     | 11.4                 | 12  | 12.6    | V    |

| Supply voltage, VSS                                                     |                      | 0   |         | V    |

| Supply voltage, VBB                                                     | -2.7                 | -3  | -3.3    | V    |

| High-level input voltage, VIH (all inputs except chip enable)           | 2.2                  |     | 5.25    | V    |

| High-level chip enable input voltage, VIH(CE)                           | V <sub>DD</sub> -0.6 | V   | DD +1.0 | V    |

| Low-level input voltage, VIL (all inputs except chip enable) (see Note) | -0.6                 |     | 0.6     | V    |

| Low-level chip enable input voltage, VIL(CE) (see Note)                 | -1                   |     | 0.6     | V    |

| Refresh time, trefresh                                                  |                      |     | 2       | ms   |

| Operating free-air temperature, TA                                      | 0                    |     | 70      | °c   |

NOTE: The algebraic convention where the most negative limit is designated as minimum is used in this data sheet for logic voltage levels only.

## electrical characteristics over full ranges of recommended operating conditions, $T_A = 0^\circ C$ to $70^\circ C$ (unless otherwise noted)

|                 | PARAMETER                                                                                                                                                                                                                                                                                                    | TEST CO                                              | NDITIONS                                           | MIN             | TYP <sup>†</sup> | MAX  | UNIT |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|-----------------|------------------|------|------|

| ∨он             | High-level output voltage                                                                                                                                                                                                                                                                                    | l <sub>O</sub> =2 mA                                 |                                                    | 2.4             |                  | Vcc  | V    |

| VOL             | Low-level output voltage                                                                                                                                                                                                                                                                                     | l <sub>O</sub> = 3.2 mA                              |                                                    | V <sub>SS</sub> |                  | 0.4  | V    |

| 1               | Input current (all inputs except chip enable)                                                                                                                                                                                                                                                                | V <sub>1</sub> = 0 to 5.25 V                         |                                                    |                 |                  | 10   | μΑ   |

| 1I(CE)          | Chip enable input current                                                                                                                                                                                                                                                                                    | V <sub>1</sub> = 0 to 13.2 V                         |                                                    |                 |                  | 2    | μA   |

| I <sub>OZ</sub> | High-impedance-state (off-state output current                                                                                                                                                                                                                                                               | V <sub>O</sub> = 0 to 5.25 V                         |                                                    |                 | 10               | μA   |      |

| ICC             | Supply current from V <sub>CC</sub>                                                                                                                                                                                                                                                                          | 2 Series 74 TTL I                                    |                                                    | _               | 1                | mA   |      |

| ססי             | Supply current from VDD                                                                                                                                                                                                                                                                                      | VIH(CE) = 12.6 \                                     |                                                    | 30              | 60               | mA   |      |

| IDD             | Supply current from VDD, standby                                                                                                                                                                                                                                                                             | VIL(CE) = 0.6 V                                      |                                                    | -               | 20               | 200  | μA   |

|                 |                                                                                                                                                                                                                                                                                                              |                                                      | TMS 4030                                           |                 | 32               |      |      |

| IDD(av)         | High-impedance-state (off-state<br>output current<br>Supply current from V <sub>CC</sub><br>Supply current from V <sub>DD</sub><br>Supply current from V <sub>DD</sub> , standby<br>Average supply current from V <sub>DD</sub><br>during read or write cycle<br>Average supply current from V <sub>DD</sub> |                                                      | TMS 4030-1                                         |                 | 35               | _    | mA   |

|                 | during read or write cycle                                                                                                                                                                                                                                                                                   | Minimum cycle                                        | TMS 4030-2                                         |                 | 38               |      |      |

|                 |                                                                                                                                                                                                                                                                                                              | time                                                 | TMS 4030                                           |                 | 32               |      | ]    |

| DD(av)          |                                                                                                                                                                                                                                                                                                              |                                                      | TMS 4030-1                                         |                 | 35               |      | mA   |

|                 | during read, modity write cycle                                                                                                                                                                                                                                                                              |                                                      | TMS 4030-2                                         |                 | 38               |      |      |

| IBB             | Supply current from V <sub>BB</sub>                                                                                                                                                                                                                                                                          | V <sub>BB</sub> =3.3 V,<br>V <sub>DD</sub> = 12.6 V, | V <sub>CC</sub> = 5.25 V,<br>V <sub>SS</sub> = 0 V |                 | -5               | -100 | μA   |

<sup>†</sup>All typical values are at  $T_A = 25^{\circ}C$

## capacitance at $V_{DD}$ = 12 V, $V_{SS}$ = 0 V, $V_{BB}$ = -3 V, $V_{CC}$ = 5 V, $V_{I(CE)}$ = 0 V, $V_{I}$ = 0 V, f = 1 MHz, $T_A$ = 0°C to 70°C (unless otherwise noted)

|          | PARAMETER                           | TEST CONDITIONS             | MIN | TYP <sup>†</sup> | MAX | UNIT |

|----------|-------------------------------------|-----------------------------|-----|------------------|-----|------|

| Ci(ad)   | Input capacitance address inputs    |                             |     | 5                | 7   | pF   |

| C        | Input capacitance clock input       | VI(CE) = 10.8 V             |     | 18               | 22  |      |

| Ci(CE)   | mput capacitance clock input        | V <sub>I(CE)</sub> = -1.0 V |     | 23               | 7   | pF   |

| Ci(CS)   | Input capacitance chip select input |                             |     | 4                | 6   | pF   |

| Ci(data) | Input capacitance data input        |                             |     | 4                | 6   | pF   |

| Ci(R/W)  | Input capacitance read/write input  |                             |     | 5                | 7   | pF   |

| Co       | Output capacitance                  |                             |     | 5                | 7   | pF   |

<sup>†</sup>All typical values are at  $T_A = 25^{\circ}$ C.

;75

# TMS 4030 JL, NL; TMS 4030-1 JL, NL; TMS 4030-2 JL, NL 4096-BIT DYNAMIC RANDOM-ACCESS MEMORIES

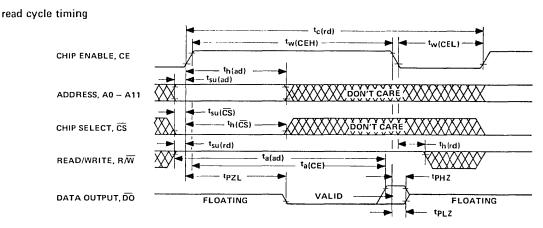

| read cycle timing requirements over recommended supply | voltage range, $T_A = 0^\circ C$ to $70^\circ C$ |

|--------------------------------------------------------|--------------------------------------------------|

|--------------------------------------------------------|--------------------------------------------------|

|                      | PARAMETER                     | TMS  | 4030 | TMS 4 | 030-1 | TMS 4 |      |    |

|----------------------|-------------------------------|------|------|-------|-------|-------|------|----|

|                      | FARAMETER                     | MIN  | MAX  | MIN   | MAX   | MIN   | MAX  |    |

| tc(rd)               | Read cycle time               | 470  |      | 430   |       | 400   |      | ns |

| <sup>t</sup> w(CEH)  | Pulse width, chip enable high | 300  | 4000 | 260   | 4000  | 230   | 4000 | ns |

| tw(CEL)              | Pulse width, chip enable low  | 130  |      | 130   |       | 130   |      | ns |

| tr(CE)               | Chip-enable rise time         |      | 40   |       | 40    |       | 40   | ns |

| tf(CE)               | Chip-enable fall time         |      | 40   |       | 40    |       | 40   | ns |

| t <sub>su(ad)</sub>  | Address setup time            | 01   |      | 01    |       | 01    |      | ns |

| t <sub>su</sub> (CS) | Chip-select setup time        | 01   |      | 10    |       | 01    |      | ns |

| t <sub>su(rd)</sub>  | Read setup time               | 0†   |      | 01    |       | 01    |      | ns |

| th(ad)               | Address hold time             | 150↑ |      | 150↑  |       | 150↑  |      | ns |

| th(CS)               | Chip-select hold time         | 150↑ |      | 150↑  | ~     | 150↑  |      | ns |

| <sup>t</sup> h(rd)   | Read hold time                | 40↓  |      | 40↓   |       | 40↓   |      | ns |

$\uparrow\downarrow$  The arrow indicates the edge of the chip enable pulse used for reference:  $\uparrow$  for the rising edge,  $\downarrow$  for the falling edge.

## read cycle switching characteristics over recommended supply voltage range, $T_A = 0^{\circ}C$ to $70^{\circ}C$

| PARAMETER           |                                              | TMS | 4030 | TMS | 4030-1 | TMS 4 |     |      |

|---------------------|----------------------------------------------|-----|------|-----|--------|-------|-----|------|

|                     | CARAMETER                                    | MIN | MAX  | MIN | MAX    | MIN   | MAX | UNIT |

| t <sub>a</sub> (CE) | Access time from chip enablet                |     | 280  |     | 230    |       | 180 | ns   |

| ta(ad)              | Access time from address t                   |     | 300  |     | 250    |       | 200 | ns   |

| tPHZ or             | Output disable time from high                |     |      |     |        |       |     |      |

| <sup>t</sup> PLZ    | or low level‡                                | 30  |      | 30  |        | 30    |     | ns   |

| tPZL.               | Output enable time to low level <sup>‡</sup> |     | 250  |     | 200    |       | 150 | ns   |

<sup>†</sup>Test conditions:  $C_L = 50 \text{ pF}$ ,  $t_{r(CE)} = 20 \text{ ns}$ , Load = 1 Series 74 TTL gate. <sup>‡</sup>Test conditions:  $C_L = 50 \text{ pF}$ , Load = 1 Series 74 TTL gate.

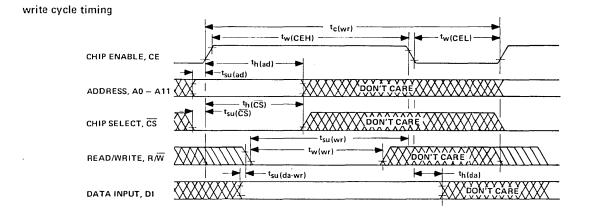

## write cycle timing requirements over recommended supply voltage range, $T_A = 0^{\circ}C$ to $70^{\circ}C$

|                                   | PARAMETER                     | TMS  | 4030 | TMS 4 | 030-1 | TMS 4 | LINIT |    |

|-----------------------------------|-------------------------------|------|------|-------|-------|-------|-------|----|

|                                   | FARAMETER                     | MIN  | MAX  | MIN   | MAX   | MIN   | MAX   |    |

| tc(wr)                            | Write cycle time              | 470  |      | 430   |       | 400   |       | ns |

| tw(CEH)                           | Pulse width, chip enable high | 300  | 4000 | 260   | 4000  | 230   | 4000  | ns |

| tw(CEL)                           | Pulse width, chip enable low  | 130  |      | 130   |       | 130   |       | ns |

| tw(wr)                            | Write pulse width             | 200  |      | 190   |       | 180   |       | ns |

| tr(CE)                            | Chip-enable rise time         |      | 40   |       | 40    |       | 40    | ns |

| tf(CE)                            | Chip-enable fall time         |      | 40   |       | 40    |       | 40    | ns |

| tsu(ad)                           | Address setup time            | 01   |      | 01    |       | 01    |       | ns |

| t <sub>su</sub> ( <del>CS</del> ) | Chip-select setup time        | 01   |      | 01    |       | 01    |       | ns |

| tsu(da-wr)                        | Data-to-write setup time*     | 0    |      | 0     |       | 0     |       | ns |

| t <sub>su(wr)</sub>               | Write-pulse setup time        | 240↓ |      | 220↓  |       | 210↓  |       | ns |

| th(ad)                            | Address hold time             | 150↑ |      | 150↑  |       | 150↑  |       | ns |

| th(CS)                            | Chip-select hold time         | 150↑ |      | 150↑  |       | 150↑  |       | ns |

| <sup>t</sup> h(da)                | Data hold time                | 40↓  |      | 40↓   |       | 40↓   |       | ns |

↑↓ The arrow indicates the edge of the chip enable pulse used for reference: ↑ for the rising edge, ↓ for the falling edge. • If R/₩ is low before CE goes high then DI must be valid when CE goes high.

## TMS 4030 JL, NL; TMS 4030-1 JL, NL; TMS 4030-2 JL, NL 4096-BIT DYNAMIC RANDOM-ACCESS MEMORIES

NOTE: For the chip-enable input, high and low timing points are 90% and 10% of V<sub>1H(CE)</sub>. Other input timing points are 0.6 V (low) and 2.2 V (high). Output timing points are 0.4 V (low) and 2.4 V (high). During the time from the rise of CE to the fall of R/W, R/W is permitted to change from high to low only.

TEXAS INSTRUMENTS POST OFFICE BOX 5012 . DALLAS, TEXAS 75222

## TMS 4030 JL, NL; TMS 4030-1 JL, NL; TMS 4030-2 JL, NL 4096-BIT DYNAMIC RANDOM-ACCESS MEMORIES

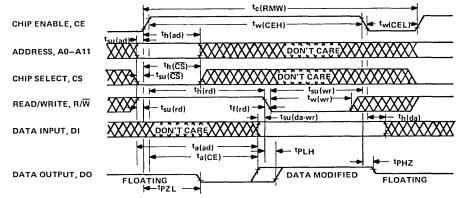

read, modify write cycle timing requirements over recommended supply voltage range,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$

|                        |                                | TMS  | 4030 | TMS  | 4030-1 | TMS 4 |      |    |

|------------------------|--------------------------------|------|------|------|--------|-------|------|----|

|                        | PARAMETER                      | MIN  | MAX  | MIN  | MAX    | MIN   | MAX  |    |

| tc(RMW)                | Read, modify write cycle time* | 710  |      | 640  |        | 580   |      | ns |

| tw(CEH)                | Pulse width, chip enable high* | 540  | 4000 | 470  | 4000   | 410   | 4000 | ns |

| tw(CEL)                | Pulse width, chip enable low   | 130  |      | 130  |        | 130   |      | ns |

| tw(wr)                 | Write-pulse width              | 200  |      | 190  |        | 180   |      | ns |

| tr(CE)                 | Chip-enable rise time          |      | 40   |      | 40     |       | 40   | ns |

| tf(CE)                 | Chip-enable fall time          |      | 40   |      | 40     |       | 40   | ns |

| t <sub>su(ad)</sub>    | Address setup time             | 0↑   |      | 10   |        | 01    |      | ns |

| t <sub>su</sub> (CS)   | Chip-select setup time         | 0↑   |      | 10   |        | 01    |      | ns |

| t <sub>su(da-wr)</sub> | Data-to-write setup time       | 0    |      | 0    |        | 0 '   |      | ns |

| t <sub>su</sub> (rd)   | Read pulse setup time          | 0↑   |      | 10   |        | 01    |      | ns |

| t <sub>su(wr)</sub>    | Write pulse setup time         | 240↓ |      | 220↓ |        | 210↓  |      | ns |

| th(ad)                 | Address hold time              | 150↑ |      | 150↑ |        | 150↑  |      | ns |

| th(CS)                 | Chip-select hold time          | 150↑ |      | 150↑ |        | 150↑  |      | ns |

| th (rd)                | Read hold time                 | 280↑ |      | 230↑ |        | 180↑  |      | ns |

| th(da)                 | Data hold time                 | 40↓  |      | 40↓  |        | 40↓   |      | ns |

$\uparrow\downarrow$  The arrow indicates the edge of the chip-enable pulse used for reference:  $\uparrow$  for the rising edge,  $\downarrow$  for the falling edge,

Test conditions: t<sub>f(rd)</sub> = 20 ns.

### read, modify write cycle switching characteristics over recommended supply voltage range, $T_A = 0^{\circ}C$ to $70^{\circ}C$

|                     |                                                                    | TMS | 4030 | TMS | 4030-1 | TMS |     |      |

|---------------------|--------------------------------------------------------------------|-----|------|-----|--------|-----|-----|------|

|                     | PARAMETER                                                          | MIN | MAX  | MIN | MAX    | MIN | MAX | UNIT |

| t <sub>a</sub> (CE) | Access time from chip enable†                                      |     | 280  |     | 230    |     | 180 | ns   |

| ta(ad)              | Access time from address t                                         |     | 300  |     | 250    |     | 200 | ns   |

| <sup>t</sup> ₽LH    | Propagation delay time, low-to-high level output from write pulse‡ | 30  |      | 30  |        | 30  |     | ns   |

| <sup>t</sup> PHZ    | Output disable time from high level ‡                              | 30  |      | 30  |        | 30  |     | ns   |

| tPZL                | Output enable time to low level <sup>‡</sup>                       |     | 250  |     | 200    |     | 150 | ns   |

<sup>†</sup>Test conditions:  $C_L = 50 \text{ pF}$ ,  $t_{r(CE)} = 20 \text{ ns}$ , Load = 1 Series 74 TTL gate. <sup>‡</sup>Test Conditions:  $C_L = 50 \text{ pF}$ , Load = 1 Series 74 TTL gate.

### read, modify write cycle timing

NOTE: For the chip enable input, high and low timing points are 90% and 10% of VIH(CE). Other input timing points are 0.6 V (low) and 2.2 V (high). Output timing points are 0.4 V (low) and 2.4 V (high).

### TMS 4030 JL, NL; TMS 4030-1 JL, NL; TMS 4030-2 JL, NL 4096-BIT DYNAMIC RANDOM-ACCESS MEMORIES

MEANING

### timing diagram conventions

TIMING DIAGRAM SYMBOL

### INPUT FORCING FUNCTIONS

Must be steady high or low

High-to-low changes permitted

Low-to-high changes permitted

Don't Care

(Does not apply)

### OUTPUT RESPONSE FUNCTIONS

Will be steady high or low

Will be changing from high to low sometime during designated interval

Will be changing from low to high sometime during designated interval

State unknown or changing

Center line is high-impedance off-state

**TYPICAL WAVEFORMS**

## TEXAS INSTRUMENTS

POST OFFICE BOX 5012 . DALLAS, TEXAS 75222

TEXAS INSTRUMENTS RESERVES THE RIGHT TO MAKE CHANGES AT ANY TIME IN ORDER TO IMPROVE DESIGN AND TO SUPPLY THE BEST PRODUCT POSSIBLE.