# DF320/DF320A/DF322 CMOS Loop Disconnect Dialers

## **B** Siliconix

#### **FEATURES**

- 2.5 V to 5.5 V Operation

- 6 μW Standby Dissipation

- Selectable M/S and Impulsing Speed

- Integrated Functions for Fewer External Components

#### **BENEFITS**

- Operates on Long and Short Loops

- Presents No Load to Voice

- Versatile

- Low Cost System Implementation

#### **APPLICATIONS**

- Push Button Telephones

- · Repertory Dialers

- Telex

- Mobile Telephones

- Emergency Number Dialers

#### DESCRIPTION

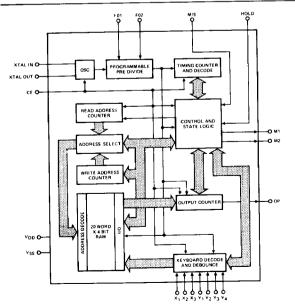

The DF320 series of monolithic CMOS Loop Disconnect Dialers each contain all the logic necessary to interface a standard double contact keyboard to a telephone system requiring loop disconnect signaling.

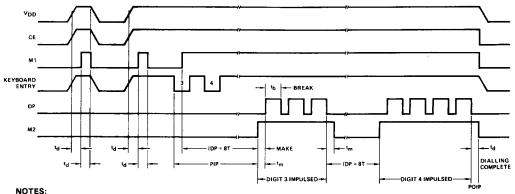

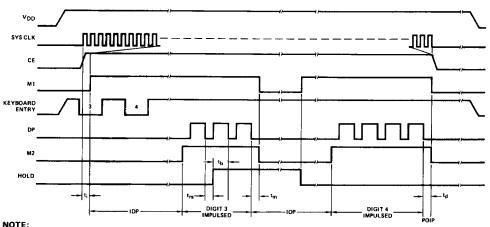

The DF320 provides the functions most commonly required in the push button telephone application. M1 is the masking option which remains at logic "1" throughout the dialing sequence. The DF322 is identical to the DF320 except that M2 is offered instead of M1. The M2 masking option is at logic "1" only during impulsing, allowing the telephone line to be monitered during the IDP. The DF320A has an extended post impulsing pause of 500 ms.

A dial pulsing output and two output options are provided to control the impulsing (loop disconnect) and muting functions. The circuit is capable of storing a number string of up to 20 digits and re-dialing this stored number automatically at a later time, initiated by a RE-DIAL input code. Impulsing mark/space ratio (M/S), and impulsing rate are pin programmable to meet most telephone authority specifications.

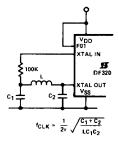

External component count is minimized by the inclusion of an on-chip clock oscillator, high impedance pull-down terminations to programming inputs as well as pull-up terminations to the keyboard giving direct interfacing.

### FUNCTIONAL BLOCK DIAGRAM

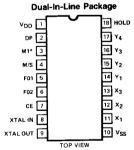

#### PIN CONFIGURATION

'M2 ON DF322DJ, DF322DK, DF322DP

Order Numbers:

DF320DJ, DF320ADJ, or DF322DJ

See Package 19

DF320DK, DF320ADK, or DF322DK

See Package 23

DF320DP, DF320ADP, DF322DP

See Package 20

### DF320/DF320A/DF322

#### ABSOLUTE MAXIMUM RATINGS

| V <sub>DD</sub> - V <sub>SS</sub> 0.3 V to 8 V |

|------------------------------------------------|

| Voltage on Any Pin VSS - 0.3 V to VDD + 0.3 V  |

| Current at Any Pin 10 mA                       |

| Operating Temperature40 to +85°C               |

| Storage Temperature (K Package)65 to +150°C    |

| (J Package)65 to +125°C                        |

Power Dissipation (J and K Package)\* ....... 450 mW

\*Derate 6.3 mW/° C above 25° C. All leads soldered to PC board.

#### ELECTRICAL CHARACTERISTICS 1, 2

$T_{\Delta} = 25^{\circ}C$

|                                                        |                           | TEST CONDITIONS                                                         | LIMITS                            |            |      |     |  |

|--------------------------------------------------------|---------------------------|-------------------------------------------------------------------------|-----------------------------------|------------|------|-----|--|

| PARAMETER                                              | SYMBOL                    | UNLESS OTHERWISE NOTED:<br>VDD = 3.0 V, f <sub>CLK</sub> = 3.579545 MHz | MIN <sup>3</sup> TYP <sup>4</sup> |            | MAX  | UN  |  |

| Supply Voltage Operating<br>Range                      | V <sub>DD</sub>           |                                                                         | 2.5                               |            | 5.5  | V   |  |

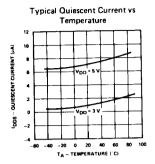

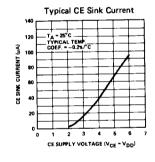

| Standby Supply Current                                 | <sup>I</sup> D <b>S</b> S | CE = V <sub>SS</sub>                                                    |                                   | 2          | 10   |     |  |

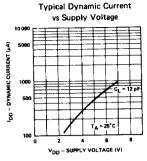

| Operating Supply Current                               | l <sub>DD</sub>           | C <sub>XTALOUT</sub> = 12 pF                                            |                                   | 155        | 250  |     |  |

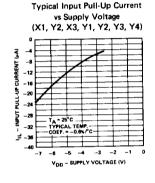

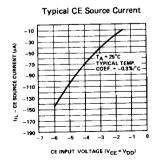

| Keypad Input Pull-Up<br>Transistor Source Current      | lirk                      | V <sub>IN</sub> = V <sub>SS</sub>                                       | -10                               | -6         | -0.5 |     |  |

| Keypad Input Leakage<br>Current                        | инк                       | V <sub>IN</sub> = V <sub>DD</sub>                                       |                                   | 0.1        |      | nA  |  |

| Programming Input<br>Leakage Current                   | lilb                      | V <sub>IN</sub> = V <sub>SS</sub>                                       |                                   | -0.1       |      |     |  |

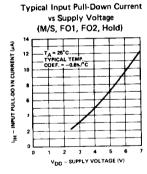

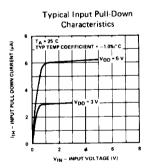

| Programming Input Pull-Down<br>Transistor Sink Current | IIHP                      | $V_{IN} = V_{DD}$                                                       | 0.5                               | 3          | 10   | μ   |  |

| Input Logic "O" Level (All Inputs)                     | VIL                       |                                                                         |                                   |            | 0.65 |     |  |

| Input Logic "I" Level<br>(All Inputs)                  | VIH                       |                                                                         | 2.45                              |            |      |     |  |

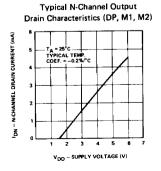

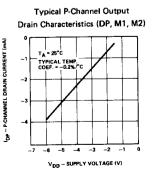

| Output Voltage Low<br>Level (DP, M1, M2)               | VOL                       | No Load                                                                 |                                   | 0          | 0.01 |     |  |

| Output Voltage High<br>Level (DP, M1, M2)              | voн                       | No Load                                                                 | 2.99                              | 3          |      |     |  |

| Output Current Low<br>Level (DP, M1, M2)               | lor                       | V <sub>OUT</sub> = +2.3 V                                               | 0.5                               | 1.5        |      |     |  |

| Output Current High<br>Level (DP, M1, M2)              | ЮН                        | V <sub>OUT</sub> = +0.7 V                                               |                                   | -1.5       | -0.5 | ] " |  |

| Output Rise Time<br>(DP, M1, M2)                       | t <sub>r</sub>            | 0 50-5                                                                  |                                   | 1          |      | Ī,  |  |

| Output Fall Time<br>(DP, M1, M2)                       | tf                        | C <sub>L</sub> = 50 pF                                                  |                                   | 1          |      | ]   |  |

| Maximum Clock Frequency                                | fCLK                      |                                                                         | 3.58                              |            |      | м   |  |

| Mark To Space Ratio                                    | M/S                       | See Table 1                                                             | 3:2                               |            | 2:1  |     |  |

| Interdigit Pause                                       | IDP                       | T = Selected Impulsing<br>Period (See Table 1)                          |                                   | 8T         |      | n   |  |

| Impulsing Rate = 1T                                    |                           | See Table 1                                                             | 10                                |            | 932  | ŀ   |  |

| Clock Start Up Time                                    | ton                       | Timed From<br>CE = Logic "I"                                            |                                   | 1.5        | 4    | n   |  |

| Input Capacitance                                      | C <sub>IN</sub>           | Any Input                                                               |                                   | 5          |      | p   |  |

| Post Impulsing Pause                                   | POIP                      | DF320, DF322<br>DF320A                                                  |                                   | 0.3T<br>5T |      | -   |  |

#### NOTES:

- 1. Refer to PROCESS OPTION FLOWCHART for additional information.

- 2. All voltages referenced to VSS unless otherwise noted.

- 3. The algebraic convention whereby the most negative value is minimum, and the most positive value is maximum, is used in this data sheet.

- 4. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

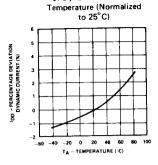

Typical Percentage Deviation of Dynamic Current vs

#### Table 1

|                                                                                                                           |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 | DESCRIPTION                                                                                                                                      |                         |           |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|--|--|--|

| VDD                                                                                                                       | Positive voltage supply                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

| DP                                                                                                                        | Dial Pulsing Output Buffer                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

| 11                                                                                                                        | Mask 1 (Buffered Output) = Logic "1" during Dialing Sequence                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

| M2                                                                                                                        | Mask 2 (Buffered Output) = Logic "1" during Impulsing                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

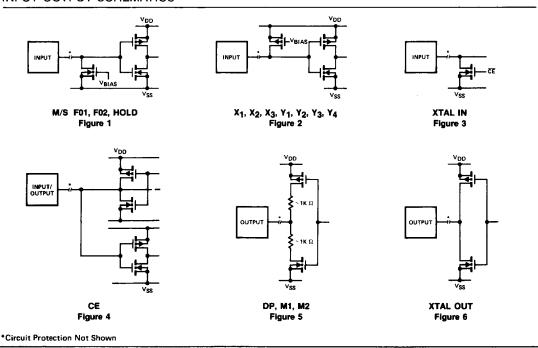

| M/S                                                                                                                       | Mark/Space (Break/Make) Ratio select. On-chip active pull-down to VSS.                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

|                                                                                                                           |                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

|                                                                                                                           | ОС                                                                                                                          | 2:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                                                                               |                                                                                                                                                  |                         |           |  |  |  |

|                                                                                                                           | V <sub>DD</sub>                                                                                                             | 3:2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                 | C = Open circuit, see                                                                                                                            | e Figure 7              |           |  |  |  |

|                                                                                                                           | <u> </u>                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

| 01, F02                                                                                                                   | Impulsing Ra                                                                                                                | ite Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n. On-chip active pul                                                                                                                                           | -down to V <sub>SS</sub> .                                                                                                                       |                         |           |  |  |  |

|                                                                                                                           |                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Nominal                                                                                                                                                         | Actual*                                                                                                                                          | System                  |           |  |  |  |

|                                                                                                                           | F01                                                                                                                         | F02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Impulsing Rate                                                                                                                                                  | Impulsing Rate                                                                                                                                   | Clock Frequency         |           |  |  |  |

|                                                                                                                           | ОС                                                                                                                          | ОС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 Hz                                                                                                                                                           | 10.13 Hz                                                                                                                                         | 303.9 Hz                |           |  |  |  |

|                                                                                                                           | ОС                                                                                                                          | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 Hz                                                                                                                                                           | 19.42 Hz                                                                                                                                         | 582.6 Hz                |           |  |  |  |

|                                                                                                                           | VDD                                                                                                                         | ОС                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 932 Hz                                                                                                                                                          | 932.17 Hz                                                                                                                                        | 27,965.1 Hz             |           |  |  |  |

|                                                                                                                           | VDD                                                                                                                         | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 Hz                                                                                                                                                           | 15.54 Hz                                                                                                                                         | 466,1 Hz                |           |  |  |  |

|                                                                                                                           | 1                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                  |                         |           |  |  |  |

|                                                                                                                           | *Assu                                                                                                                       | mes fCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.579545 MHz                                                                                                                                                    |                                                                                                                                                  |                         |           |  |  |  |

| E                                                                                                                         |                                                                                                                             | Input/Outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 | ernally controlled by                                                                                                                            | y keyboard decode logic | . Can be  |  |  |  |

|                                                                                                                           | Chip Enable.<br>manually ena                                                                                                | Input/Outp<br>bling chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | out, left open it is in                                                                                                                                         | ernally controlled by                                                                                                                            |                         | :. Can be |  |  |  |

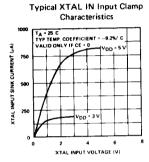

| AL IN                                                                                                                     | Chip Enable<br>manually ena<br>Crystal Input                                                                                | Input/Outpubling chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | out, left open it is in                                                                                                                                         | 0", high impedance i                                                                                                                             |                         | :. Can be |  |  |  |

| TAL IN                                                                                                                    | Chip Enable<br>manually ena<br>Crystal Input                                                                                | Input/Outp<br>bling chip.<br>L. Active, cla<br>ut. Buffer to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | out, left open it is in                                                                                                                                         | 0", high impedance i                                                                                                                             |                         | :. Can be |  |  |  |

| TAL IN<br>TAL OUT                                                                                                         | Chip Enable,<br>manually ena<br>Crystal Input<br>Crystal Outp<br>System grout                                               | Input/Outpubling chip.  Active, cli  ut. Buffer to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | out, left open it is in<br>amped low if CE = "1<br>o drive crystal. Capa                                                                                        | 0", high impedance i                                                                                                                             | 1 CE = "1".             | :. Can be |  |  |  |

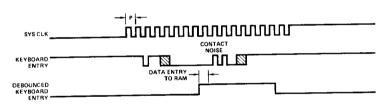

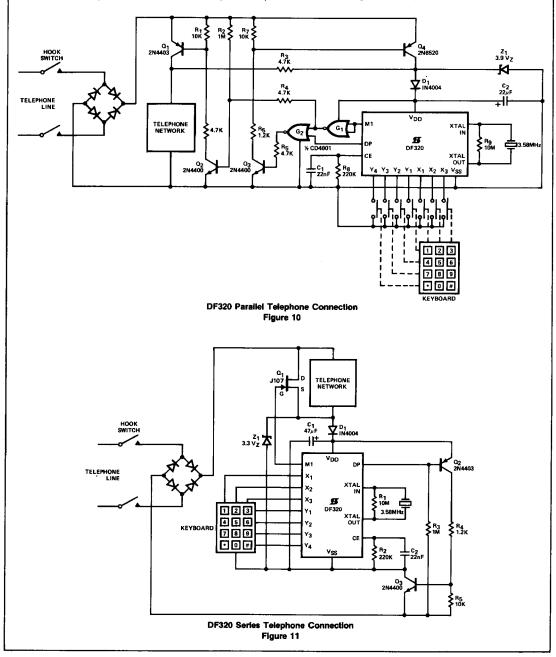

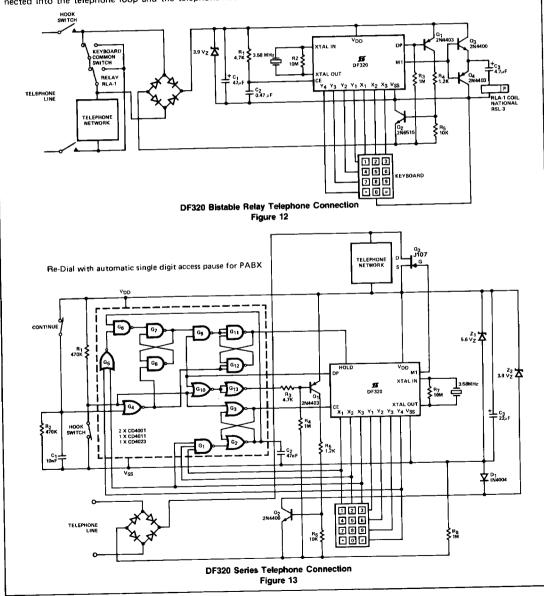

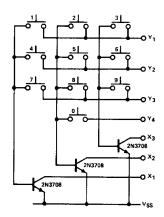

| TAL IN TAL OUT SS 1, X2, X3                                                                                               | Chip Enable,<br>manually ena<br>Crystal Input<br>Crystal Outp<br>System grout<br>Column keyt                                | Input/Outpubling chip, t. Active, cli ut. Buffer to and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | out, left open it is in<br>amped low if CE = "<br>o drive crystal. Capa<br>having active pull-u                                                                 | 0", high impedance in<br>citive load on-chip.<br>ps to V <sub>DD</sub> . Active L                                                                | f CE = "1".             | :. Can be |  |  |  |