CA-3086

General Purpose NPN Transistor Array

FN483 Rev.6.00 December 15, 2011

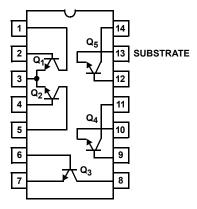

The CA3086 consists of five general-purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially connected pair.

The transistors of the CA3086 are well suited to a wide variety of applications in low-power systems at frequencies from DC to 120MHz. They may be used as discrete transistors in conventional circuits. However, they also provide the very significant inherent advantages unique to integrated circuits, such as compactness, ease of physical handling and thermal matching.

## **Ordering Information**

| PART NUMBER<br>(BRAND) | TEMP.<br>RANGE (°C) | PACKAGE                     | PKG.<br>DWG.# |

|------------------------|---------------------|-----------------------------|---------------|

| CA3086                 | -55 to 125          | 14 Ld PDIP                  | E14.3         |

| CA3086M96<br>(3086)    | -55 to 125          | 14 Ld SOIC Tape<br>and Reel | M14.15        |

# **Applications**

- Power Applications from DC to 120MHz

- General-Purpose Use in Signal Processing Systems Operating in the DC to 190MHz Range

- · Temperature Compensated Amplifiers

- See Application Note, AN5296 "Application of the CA3018 Integrated-Circuit Transistor Array" for Suggested Applications

### **Pinout**

#### CA3086 (PDIP, SOIC) TOP VIEW

## **Absolute Maximum Ratings**

| The following ratings apply for each transistor in the device: |

|----------------------------------------------------------------|

| Collector-to-Emitter Voltage, V <sub>CEO</sub>                 |

| Collector-to-Base Voltage, V <sub>CBO</sub>                    |

| Collector-to-Substrate Voltage, V <sub>CIO</sub> (Note 1)20    |

| Emitter-to-Base Voltage, V <sub>EBO</sub>                      |

| Collector Current, I <sub>C</sub>                              |

### **Thermal Information**

| Thermal Resistance (Typical, Note 2)     | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (oC/W)               |

|------------------------------------------|----------------------|--------------------------------------|

| PDIP Package                             | 110                  | N/A                                  |

| SOIC Package                             | 130                  | N/A                                  |

| Maximum Power Dissipation (Any one train | nsistor)             | 300mW                                |

| Maximum Junction Temperature (Plastic F  | Package)             | 150°C                                |

| Maximum Storage Temperature Range .      | 65                   | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1    | 0s)                  | 300°C                                |

| (SOIC - Lead Tips Only)                  |                      |                                      |

### **Operating Conditions**

Temperature Range.....-55°C to 125°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. The collector of each transistor in the CA3086 is isolated from the substrate by an integral diode. The substrate (Terminal 13) must be connected to the most negative point in the external circuit to maintain isolation between transistors and to provide for normal transistor action. To avoid undesirable coupling between transistors, the substrate (Terminal 13) should be maintained at either DC or signal (AC) ground. A suitable bypass capacitor can be used to establish a signal ground.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** $T_A = 25^{\circ}C$ , For Equipment Design

| PARAMETER                                    | SYMBOL               | TEST CONDITIONS                            | MIN | TYP        | MAX | UNITS |

|----------------------------------------------|----------------------|--------------------------------------------|-----|------------|-----|-------|

| Collector-to-Base Breakdown Voltage          | V <sub>(BR)CBO</sub> | $I_C = 10\mu A, I_E = 0$                   | 20  | 60         | -   | V     |

| Collector-to-Emitter Breakdown Voltage       | V <sub>(BR)CEO</sub> | I <sub>C</sub> = 1mA, I <sub>B</sub> = 0   | 15  | 24         | -   | V     |

| Collector-to-Substrate Breakdown Voltage     | V <sub>(BR)CIO</sub> | $I_C = 10\mu A, I_{CI} = 0$                | 20  | 60         | -   | V     |

| Emitter-to-Base Breakdown Voltage            | V <sub>(BR)EBO</sub> | $I_E = 10\mu A, I_C = 0$                   | 5   | 7          | -   | V     |

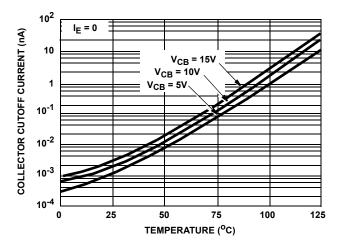

| Collector-Cutoff Current (Figure 1)          | I <sub>CBO</sub>     | $V_{CB} = 10V, I_E = 0,$                   | -   | 0.002      | 100 | nA    |

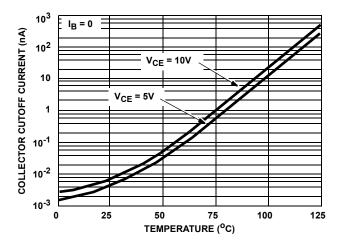

| Collector-Cutoff Current (Figure 2)          | I <sub>CEO</sub>     | V <sub>CE</sub> = 10V, I <sub>B</sub> = 0, | -   | (Figure 2) | 5   | μΑ    |

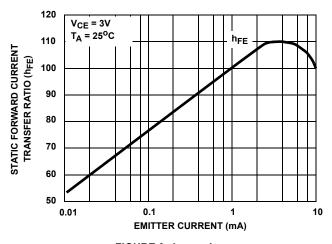

| DC Forward-Current Transfer Ratio (Figure 3) | h <sub>FE</sub>      | $V_{CE} = 3V$ , $I_{C} = 1mA$              | 40  | 100        | -   |       |

## **Electrical Specifications** $T_A = 25^{\circ}C$ , Typical Values Intended Only for Design Guidance

| PARAMETER                                                               | SYMBOL                | TEST CONDITIONS                                                      |                       | TYPICAL<br>VALUES | UNITS              |

|-------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|-----------------------|-------------------|--------------------|

| DC Forward-Current Transfer Ratio                                       | h <sub>FE</sub>       | V <sub>CE</sub> = 3V                                                 | I <sub>C</sub> = 10mA | 100               |                    |

| (Figure 3)                                                              |                       |                                                                      | $I_C = 10\mu A$       | 54                |                    |

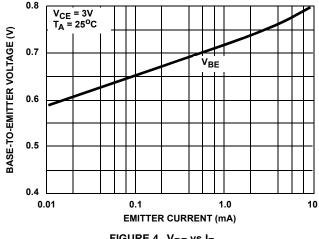

| Base-to-Emitter Voltage (Figure 4) V <sub>BE</sub> V <sub>CE</sub> = 3V | I <sub>E</sub> = 1 mA | 0.715                                                                | V                     |                   |                    |

|                                                                         |                       |                                                                      | I <sub>E</sub> = 10mA | 0.800             | V                  |

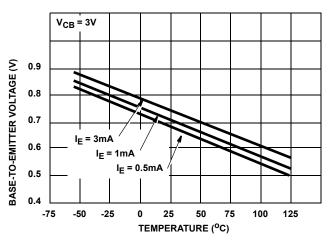

| V <sub>BE</sub> Temperature Coefficient (Figure 5)                      | ΔV <sub>BE</sub> /ΔΤ  | V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                          |                       | -1.9              | mV/ <sup>o</sup> C |

| Collector-to-Emitter<br>Saturation Voltage                              | V <sub>CE</sub> SAT   | I <sub>B</sub> = 1mA, I <sub>C</sub> = 10mA                          |                       | 0.23              | V                  |

| Noise Figure (Low Frequency)                                            | NF                    | $f = 1kHz$ , $V_{CE} = 3V$ , $I_{C} = 100\mu A$ , $R_{S} = 1k\Omega$ |                       | 3.25              | dB                 |

## **Electrical Specifications** $T_A = 25^{\circ}C$ , Typical Values Intended Only for Design Guidance (Continued)

| PARAMETER                                                           | SYMBOL           | TEST CONDITIONS                                     | TYPICAL<br>VALUES      | UNITS |

|---------------------------------------------------------------------|------------------|-----------------------------------------------------|------------------------|-------|

| Low-Frequency, Small-Signal Equivalent-<br>Circuit Characteristics: |                  | $f = 1kHz, V_{CE} = 3V, I_{C} = 1mA$                |                        |       |

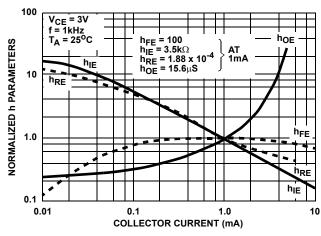

| Forward Current-Transfer Ratio (Figure 6)                           | h <sub>FE</sub>  |                                                     | 100                    | -     |

| Short-Circuit Input Impedance (Figure 6)                            | h <sub>IE</sub>  |                                                     | 3.5                    | kΩ    |

| Open-Circuit Output Impedance (Figure 6)                            | hOE              |                                                     | 15.6                   | μS    |

| Open-Circuit Reverse-Voltage<br>Transfer Ratio (Figure 6)           | h <sub>RE</sub>  |                                                     | 1.8 X 10 <sup>-4</sup> | -     |

| Admittance Characteristics:                                         |                  | f = 1MHz,V <sub>CE</sub> = 3V, I <sub>C</sub> = 1mA |                        |       |

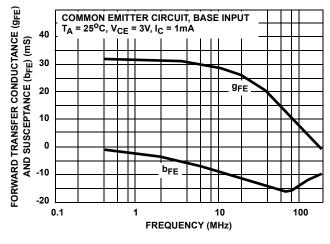

| Forward Transfer Admittance (Figure 7)                              | УFЕ              |                                                     | 31 - j1.5              | mS    |

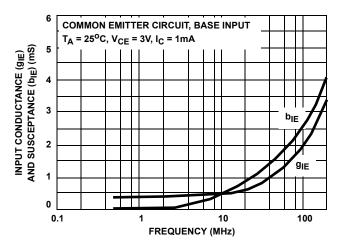

| Input Admittance (Figure 8)                                         | УІЕ              |                                                     | 0.3 + j0.04            | mS    |

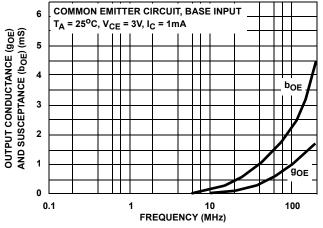

| Output Admittance (Figure 9)                                        | УОЕ              |                                                     | 0.001 + j0.03          | mS    |

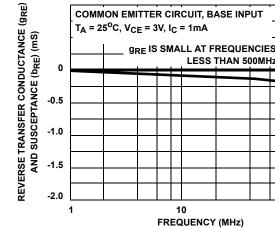

| Reverse Transfer Admittance (Figure 10)                             | УRЕ              |                                                     | See Figure 10          | -     |

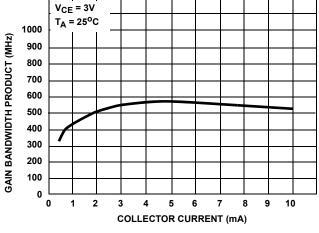

| Gain-Bandwidth Product (Figure 11)                                  | f <sub>T</sub>   | V <sub>CE</sub> = 3V, I <sub>C</sub> = 3mA          | 550                    | MHz   |

| Emitter-to-Base Capacitance                                         | C <sub>EBO</sub> | V <sub>EB</sub> = 3V, I <sub>E</sub> = 0            | 0.6                    | pF    |

| Collector-to-Base Capacitance                                       | C <sub>CBO</sub> | V <sub>CB</sub> = 3V, I <sub>C</sub> = 0            | 0.58                   | pF    |

| Collector-to-Substrate Capacitance                                  | C <sub>CIO</sub> | V <sub>C I</sub> = 3V, I <sub>C</sub> = 0           | 2.8                    | pF    |

# **Typical Performance Curves**

FIGURE 1.  $I_{\mbox{\footnotesize{CBO}}}$  vs TEMPERATURE

FIGURE 2.  $I_{\mbox{\footnotesize{CEO}}}$  vs TEMPERATURE

## Typical Performance Curves (Continued)

FIGURE 3. hFE vs IE

FIGURE 4. VBE vs IE

FIGURE 5. VBE vs TEMPERATURE

FIGURE 6. NORMALIZED  $h_{\mbox{\scriptsize FE}}, h_{\mbox{\scriptsize IE}}, h_{\mbox{\scriptsize RE}}, h_{\mbox{\scriptsize OE}}$  vs  $I_{\mbox{\scriptsize C}}$

FIGURE 7. y<sub>FE</sub> vs FREQUENCY

FIGURE 8. y<sub>IE</sub> vs FREQUENCY

# Typical Performance Curves (Continued)

FIGURE 10. y<sub>RE</sub> vs FREQUENCY

COMMON EMITTER CIRCUIT, BASE INPUT

gre IS SMALL AT FREQUENCIES

LESS THAN 500MHz

bRE

100

$T_A = 25^{\circ}C$ ,  $V_{CE} = 3V$ ,  $I_C = 1mA$

0

-0.5

-1.0

FIGURE 11. f<sub>T</sub> vs I<sub>C</sub>

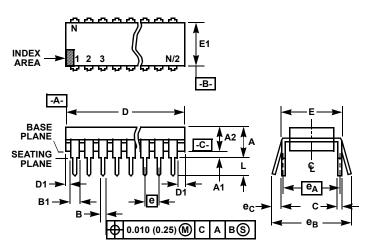

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and  $\boxed{e_A}$  are measured with the leads constrained to be perpendicular to datum  $\boxed{-C}$ .

- e<sub>B</sub> and e<sub>C</sub> are measured at the lead tips with the leads unconstrained. e<sub>C</sub> must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E14.3 (JEDEC MS-001-AA ISSUE D)

14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES |       | MILLIMETERS |       |       |

|----------------|--------|-------|-------------|-------|-------|

| SYMBOL         | MIN    | MAX   | MIN         | MAX   | NOTES |

| Α              | -      | 0.210 | -           | 5.33  | 4     |

| A1             | 0.015  | -     | 0.39        | -     | 4     |

| A2             | 0.115  | 0.195 | 2.93        | 4.95  | -     |

| В              | 0.014  | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.045  | 0.070 | 1.15        | 1.77  | 8     |

| С              | 0.008  | 0.014 | 0.204       | 0.355 | -     |

| D              | 0.735  | 0.775 | 18.66       | 19.68 | 5     |

| D1             | 0.005  | -     | 0.13        | -     | 5     |

| Е              | 0.300  | 0.325 | 7.62        | 8.25  | 6     |

| E1             | 0.240  | 0.280 | 6.10        | 7.11  | 5     |

| е              | 0.100  | BSC   | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.300  | BSC   | 7.62 BSC    |       | 6     |

| e <sub>B</sub> | -      | 0.430 | -           | 10.92 | 7     |

| L              | 0.115  | 0.150 | 2.93        | 3.81  | 4     |

| N              | 1      | 4     | 14          |       | 9     |

Rev. 0 12/93

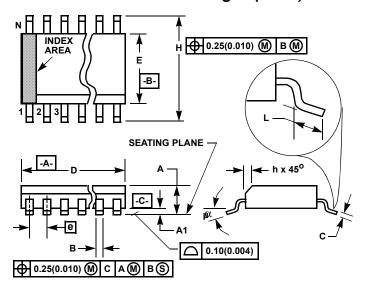

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M14.15 (JEDEC MS-012-AB ISSUE C)

14 LEAD NARROW BODY SMALL OUTLINE PLASTIC

PACKAGE

|        | INCHES |                | MILLIM   |      |       |  |

|--------|--------|----------------|----------|------|-------|--|

| SYMBOL | MIN    | MAX            | MIN      | MAX  | NOTES |  |

| Α      | 0.0532 | 0.0688         | 1.35     | 1.75 | -     |  |

| A1     | 0.0040 | 0.0098         | 0.10     | 0.25 | -     |  |

| В      | 0.013  | 0.020          | 0.33     | 0.51 | 9     |  |

| С      | 0.0075 | 0.0098         | 0.19     | 0.25 | -     |  |

| D      | 0.3367 | 0.3444         | 8.55     | 8.75 | 3     |  |

| E      | 0.1497 | 0.1574         | 3.80     | 4.00 | 4     |  |

| е      | 0.050  | BSC            | 1.27 BSC |      | -     |  |

| Н      | 0.2284 | 0.2440         | 5.80     | 6.20 | -     |  |

| h      | 0.0099 | 0.0196         | 0.25     | 0.50 | 5     |  |

| L      | 0.016  | 0.050          | 0.40     | 1.27 | 6     |  |

| N      | 14     |                | 1        | 4    | 7     |  |

| α      | 0°     | 8 <sup>o</sup> | 0°       | 8º   | -     |  |

Rev. 0 12/93

© Copyright Intersil Americas LLC 2003-2011. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>